Some things regarding Handout 11 Q2:

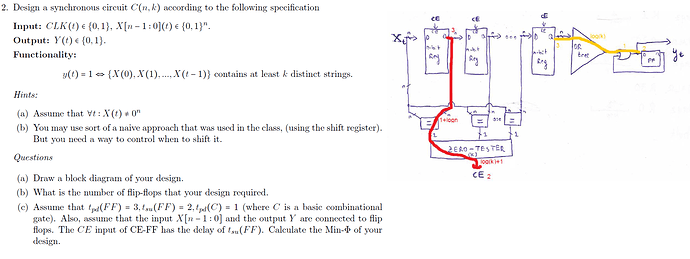

Here is the question and the attached solution which was posted

-

How is the design correct if we get an input vector which is not different? It seems like will then still get y=1 rather than y=0

-

How many registers are there in here? Because if there is one for every time iteration then that makes no sense since that means the amount changes over time and what is sketched here is just not something I can actually design

-

The delay path is marked in red. How is that the longest path if it does not start with an input and ends with an output?