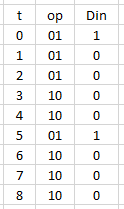

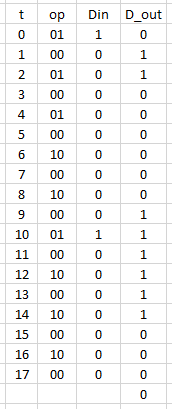

I’m having a hard time understanding figure 4,

is it possible is this implementation to push one bit and then pop it?

walkthrough (as i understand it):

if i enter first bit 1 (op=01), it instantly arrives at v1 (t=0), after 1 tick (t=1) the bit is between the two FF.

now i try to pop (op=10, t=2, bit 1 is at v2) because of the lag(1), v2 thinks it needs to push, so it pushes it to R_out

only at cycle 3, after the bit has crossed over to v3, it sent back, stuck at the FF before v2,

so if i understand correctly the bit arrives back to v1 only after 4 clock cycles.

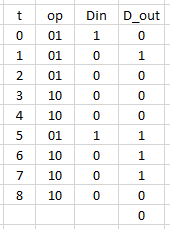

this can be resolved if v2 will send the bit both to R_out and v1, regardless of the op.

in this scenario:

- do i care about the “rouge” bit crossed to v3?

- does the implementation suppose to support modification? meaning popping some of the bits then pushing new ones (in contrast to popping them all together)

because if it supports modifying, how will v1 choose what bit to push, the one from L_in or the one from v2?

thank you very much